A "test beuch" is a veilog program that can drive a verilog (or any) circuit, simulating the impuls to that circuit to test the response

Response: 1. "fanctional" - test the logic

2. timing - to make sure things happen

When they should

#1 is reasy #2 is only as good as the ability to simulate actual timing

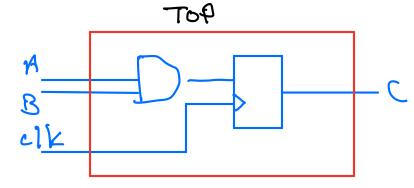

ex circuit to test:

verilog code:

module top (

input A, B, clk,

output reg C);

```

wire d = A&B;

always @ (posedge clk) C <= d;

end module

```

verilog test beuch:

'timescale Ins/1ps module top-tb;

timescale a/b ('= backguote, no; at end)

a = time unit

b = precision

time units are used w/ # sign in verilog to add a delay

a=0; #1 a=1; #5 a=0;

this means 1. set a=0

2. wait l'fick" (Ins) and then set a=1

3. wait 5 ns and set a=0

Next: ne need to define in puts ? outputs to the circuit

circuit inputs: A,B, c/k

we need to drive these from the text bench

so fley will be reg's

reg a,h, clock;  $\geq$  names do not have circuit outputs: C to match! the test bench looks at C which is driven by the circuit

now we instantiate the circuit:

top MYTOP (.A(a), .B(b), .clk(clock),

Circuit module

name instantiation, name (any fling!)

now we need to drive the inputs lets say we want a 1 kHz clock

```

=> period is lus = 10 ns or 10 ticks

always begin

clock = 0; start at $

the 500000 clock = 1; set to 1 after forever

10 200000; 10 200000; 10 20000000;

wait 1/2 us

end

now we have to specify A,B inputs

initial begin

\alpha = 0

# 50000000 a=1; after S us, set a=1

# 20000000 b=1; after 2 us, set b=1

end

so input looks like this

then you should see G do this

```

poceage of